## Am27S23/Am27S23A

## 2,048-Bit (256x8) Bipolar PROM

## **DISTINCTIVE CHARACTERISTICS**

- High Speed

- Highly reliable, ultra-fast programming Platinum-Silicide fuses

- High programming yield

- Low-current PNP inputs

- High-current open-collector and three-state outputs

- Fast chip select

## **GENERAL DESCRIPTION**

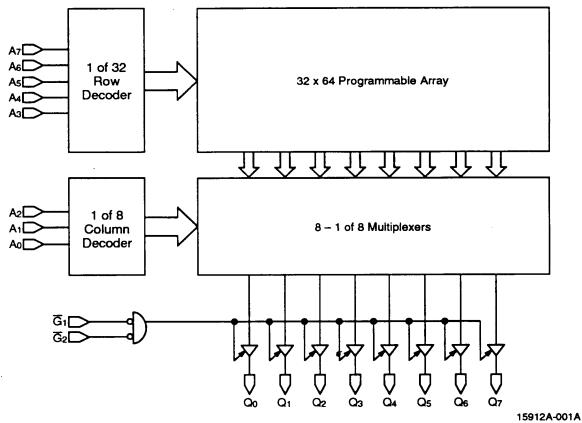

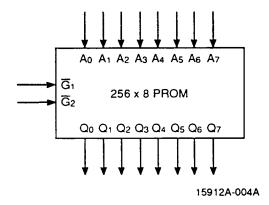

The Am27S23 (256-words by 8-bits) is a Schottky TTL Programmable Read-Only Memory (PROM).

This device has three-state outputs, compatible with low-power Schottky bus standards capable of satisfying

the requirements of a variety of microprogrammable controls, mapping functions, code conversion, or logic replacement. Easy word depth expansion is facilitated by active LOW  $(\overline{G}_1, \overline{G}_2)$  output enables.

## **FUNCTIONAL BLOCK DIAGRAM**

## PRODUCT SELECTOR GUIDE

| Three-State<br>Part Number | Am2   | 7S23A | Am27S23 |       |  |  |

|----------------------------|-------|-------|---------|-------|--|--|

| Address Access Time        | 30 ns | 40 ns | 45 ns   | 50 ns |  |  |

| Operating Range            | C     | М     | С       | М     |  |  |

Publication# 15912 Rev. A Amendment/0 Issue Date: August 1991

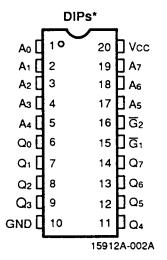

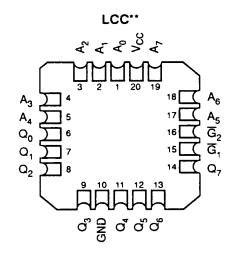

## CONNECTION DIAGRAMS

## **Top View**

Note: Pin 1 is marked for orientation.

15912A-003A

- \*Also available in a 20-pin Flatpack. Pinout identical to DIPs.

- \*\*Also available in a 20-pin PLCC. Pinout identical to LCC

## LOGIC SYMBOL

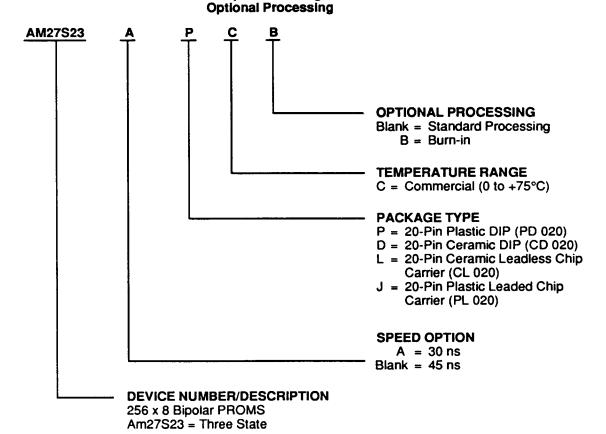

## ORDERING INFORMATION Standard Products

AMD products are available in several packages and operating ranges. The ordering number (Valid Combination)

is formed by a combination of:

Device Number

Speed Option (if applicable)

Package Type

Temperature Range

| Valid Combinations |                                       |  |  |  |  |

|--------------------|---------------------------------------|--|--|--|--|

| AM27S23            | PC, PCB, DC, DCB,                     |  |  |  |  |

| AM27S23A           | PC, PCB, DC, DCB,<br>LC, LCB, JC, JCB |  |  |  |  |

#### **Valid Combinations**

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

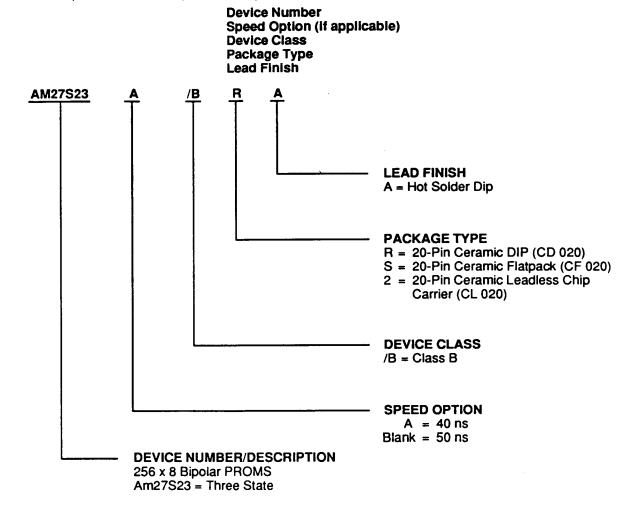

# ORDERING INFORMATION APL Products

AMD programmable logic products for Aerospace and Defense applications are available with several ordering options. APL (Approved Products List) products are fully compliant with MIL-STD-883 requirements. The order number (Valid Combination) is formed by a combination of:

| Valid Combinations |                  |  |  |  |  |

|--------------------|------------------|--|--|--|--|

| AM27S23            | /BRA, /BSA, /B2A |  |  |  |  |

| AM27S23A           | /BNA, /BSA, /BZA |  |  |  |  |

## **Valid Combinations**

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

Note: Marked with AMD logo.

Group A Tests

Group A Tests consist of Subgroups: 1, 2, 3, 7, 8, 9, 10, 11.

#### Military Burn-In

Military burn-in is in accordance with the current revision of MIL-STD-883, Test Methods 1015, Conditions A through E. Test conditions are selected at AMD's option.

## PIN DESCRIPTION

#### $A_0 - A_7$

## Address (inputs)

The 9-bit field presented at the address inputs selects one of 256 memory locations to be read from.

## Q0- Q7

## **Data Output Port**

The outputs whose state represents the data read from the selected memory locations.

## $\overline{G}_1$ , $\overline{G}_2$

## **Output Enables (Input)**

Provides direct control of the Q-output buffers. Outputs disabled forces all three-state outputs to a floating or high-impedance state.

Enable  $= \overline{G}$

Disable = G

## Vcc

## **Device Power Supply Pin**

The most positive of the logic power supply pins.

#### GND

## **Device Power Supply Pin**

The most negative of the logic power supply pins.

## **ABSOLUTE MAXIMUM RATINGS**

Storage Temperature

-65°C to +150°C

**Ambient Temperature**

with Power Applied

-55°C to +125°C

Supply Voltage with

Respect to Ground

-0.5 V to +7.0 V

DC Voltage Applied to Outputs

(Except During Programming) -0.5 V to Vcc Max.

DC Voltage Applied to Outputs

During Programming

21 V

Output Current into Outputs During

Programming (Max. Duration of 1 sec)

DC Input Voltage DC Input Current

-0.5 V to +5.5 V -30 mA to +5 mA

250 mA

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings may be supposed to the second se

mum Ratings for extended periods may affect device reliabil-

ity. Programming conditions may differ.

## **OPERATING RANGES**

#### Commercial (C) Devices

Ambient Temperature (T<sub>A</sub>)

0 to +75°C

Supply Voltage (Vcc)

+4.75 V to +5.25 V

#### Military (M) Devices\*

Case Temperature (Tc)

-55 to +125°C

Supply Voltage (Vcc)

+4.5 V to +5.5 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

\*Military product 100% tested at  $T_C = +25$ °C, +125°C, and -55°C

# DC CHARACTERISTICS over operating ranges unless otherwise specified (for APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter<br>Symbol         | Parameter Description        | Test Conditions                                                                                                                                                       | Min. | Тур. | Max.      | Unit |

|-----------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----------|------|

| V <sub>OH</sub><br>(Note 1) | Output HIGH Voltage          | V <sub>CC</sub> = Min., I <sub>OH</sub> = -2.0 mA<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub>                                                             | 2.4  |      |           | V    |

| Vol                         | Output LOW Voltage           | V <sub>CC</sub> = Min., I <sub>OH</sub> = 16 mA<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub>                                                               |      |      | 0.50      | V    |

| Viн                         | Input HIGH Level             | Guaranteed input Logical HIGH voltage for all outputs (Note 2)                                                                                                        | 2.0  |      |           | V    |

| ViL                         | Input LOW Level              | Guaranteed input logical LOW voltage for all inputs (Note 2)                                                                                                          |      |      | 0.8       | ٧    |

| lıL                         | Input LOW Current            | V <sub>CC</sub> = Max., V <sub>IN</sub> = 0.45 V                                                                                                                      |      |      | -0.250    | mA   |

| lıн                         | Input HIGH Current           | Vcc = Max., Vin = 2.7 V                                                                                                                                               |      |      | 25        | μА   |

| Isc<br>(Note 1)             | Output Short-Circuit Current | Vcc = Max., Vout = 0.0 V<br>(Note 3)                                                                                                                                  | -20  |      | -90       | mA   |

| Icc                         | Power Supply Current         | All inputs = GND, Vcc = Max.                                                                                                                                          |      |      | 160       | mA   |

| Vı                          | Input Clamp Voltage          | Vcc = Min., I <sub>IN</sub> = -18 mA                                                                                                                                  |      |      | -1.2      | V    |

| ICEX                        | Output Leakage Current       | $\begin{array}{c c} V_{CC} = Max \\ V\overline{G}_1 = 2.4 \text{ V} \end{array} \text{(Note 1)} \begin{array}{c} V_O = V_{CC} \\ V_{OUT} = 0.4 \text{ V} \end{array}$ |      |      | 40<br>-40 | μА   |

| Cin                         | Input Capacitance            | V <sub>IN</sub> = 2.0 V @ f = 1 MHz<br>(Note 4) V <sub>CC</sub> = 5 V; T <sub>A</sub> = 25°C                                                                          |      | 4    |           | pF   |

| Соит                        | Output Capacitance           | Vout = 2.0 V @ f = 1 MHz<br>(Note 4) Vcc = 5 V; Ta = 25°C                                                                                                             |      | 8    |           | ] "  |

#### Notes:

- This applies to three-state devices only.

- 2. VIL and VIH are input conditions of output tests and are not themselves directly tested. VIL and VIH are absolute voltages with respect to device ground and include all overshoots due to system and/or tester noise. Do not attempt to test these values without suitable equipment.

- 3. Not more than one output should be shorted at a time. Duration of the short circuit should not be more than one second.

- These parameters are not 100% tested, but are periodically evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

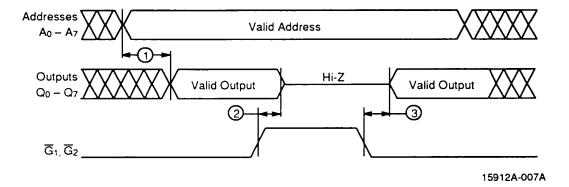

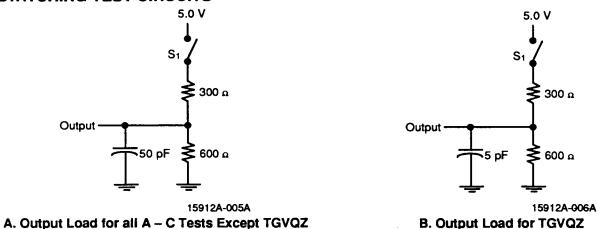

## SWITCHING CHARACTERISTICS over operating ranges unless otherwise specified (for APL Products, Group A, Subgroups 9, 10, 11 are tested unless otherwise noted\*)

| Param |           | ameter Parameter                               | "A" Version |      |      | Standard Version |       |      |      |      |       |

|-------|-----------|------------------------------------------------|-------------|------|------|------------------|-------|------|------|------|-------|

|       | Parameter |                                                | COM'L       |      | MIL  |                  | COM'L |      | MIL  |      |       |

| No.   | Symbol    | Description                                    | MIn.        | Max. | Min. | Max.             | Min.  | Max. | Mln. | Max. | Units |

| 1     | TAVQV     | Address Valid to Output Valid Access Time      |             | 30   |      | 40               |       | 45   |      | 50   | ns    |

| 2     | TGVQZ     | Delay from Output Enable Valid to Output Hi-Z  |             | 25   |      | 30               |       | 25   |      | 30   | ns    |

| 3     | TGVQV     | Delay from Output Enable Valid to Output Valid |             | 25   |      | 30               |       | 25   |      | 30   | ns    |

See also Switching Test Circuits.

#### Notes:

- 1. Tests are performed with input transition time of 5 ns or less, timing reference levels of 1.5 V, and input pulse levels of 0 to 3.0 V using test load in Figure A.

- 2. TGVQZ is measured at steady state HIGH output voltage -0.5 V and steady state LOW output voltage +0.5 V output levels using the test load in Figure B.

<sup>\*</sup>Subgroups 7 and 8 apply to functional tests.

## Notes:

- 1. All device test loads should be located within 2" of device output pin.

- 2. S1 is open for Output Data High to Hi-Z and Hi-Z to Output Data High tests. S1 is closed for all other AC tests.

- 3. Load capacitance includes all stray and fixture capacitance.

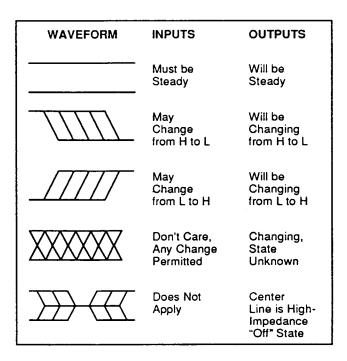

## **KEY TO SWITCHING WAVEFORMS**

KS000010